Le concept de hiérarchie de mémoire et de mémoire cache est essentiel dans l’architecture des ordinateurs modernes. Cette hiérarchie vise à optimiser les performances du système en réduisant le temps d’accès aux données fréquemment utilisées. Pour comprendre en profondeur ce sujet, nous explorerons les différentes couches de la hiérarchie de mémoire et le rôle crucial de la mémoire cache.

Au sommet de la hiérarchie se trouve la mémoire principale, également connue sous le nom de RAM (Random Access Memory). Cette mémoire est rapide mais relativement coûteuse et présente une capacité limitée. Elle stocke les données et les instructions qui sont actuellement utilisées par le processeur. Cependant, même avec sa rapidité, la mémoire principale peut ne pas être suffisamment rapide pour répondre aux demandes constantes du processeur.

Pour pallier cette limitation, les concepteurs d’architectures informatiques ont introduit la notion de mémoire cache. La mémoire cache est une mémoire de petite taille mais très rapide, placée entre le processeur et la mémoire principale. Son rôle principal est de stocker les données et les instructions les plus fréquemment utilisées par le processeur, réduisant ainsi le temps nécessaire pour accéder à ces informations.

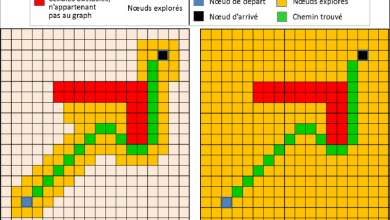

La mémoire cache fonctionne selon le principe de localité, qui se divise en deux types principaux : la localité de référence spatiale et la localité de référence temporelle. La localité de référence spatiale se réfère au fait que les données proches dans le temps ont tendance à être proches dans l’espace mémoire. En d’autres termes, si une donnée est accédée, il est probable que les données voisines soient également accédées bientôt. La localité de référence temporelle, quant à elle, fait référence au fait que les données récemment accédées ont tendance à être accédées à nouveau dans un proche avenir.

La mémoire cache est organisée en plusieurs niveaux, généralement désignés comme L1, L2 et parfois L3. L1 étant la plus proche du processeur et la plus rapide, mais aussi la plus petite en capacité, tandis que L2 et L3 sont de plus grandes tailles mais un peu plus lentes. Le processeur consulte d’abord la mémoire cache L1, puis L2 et éventuellement L3, avant d’accéder à la mémoire principale si les données nécessaires ne sont pas trouvées dans les niveaux de cache supérieurs.

Le mécanisme de gestion de la mémoire cache repose sur des algorithmes de remplacement et de localisation. Les algorithmes de remplacement déterminent quelles données doivent être supprimées de la mémoire cache pour faire de la place aux nouvelles données. Les algorithmes de localisation déterminent où placer les nouvelles données dans la mémoire cache.

Un aspect crucial de la mémoire cache est son associativité, qui décrit comment les blocs de données de la mémoire principale sont mappés sur les ensembles de la mémoire cache. Les trois principales méthodes d’associativité sont la correspondance directe, l’associativité totale et l’associativité par ensemble. Chacune de ces méthodes a ses avantages et ses inconvénients en termes de complexité et d’efficacité.

En résumé, la hiérarchie de mémoire et la mémoire cache jouent un rôle essentiel dans l’optimisation des performances des systèmes informatiques en réduisant les temps d’accès aux données fréquemment utilisées. En comprenant les principes de localité, d’associativité et les algorithmes de gestion de la mémoire cache, les concepteurs peuvent créer des architectures plus efficaces et plus performantes.

Plus de connaissances

Pour approfondir notre compréhension de la hiérarchie de mémoire et de la mémoire cache dans l’architecture informatique, explorons quelques concepts avancés et considérations pratiques.

-

Politiques de remplacement de la mémoire cache : Les politiques de remplacement déterminent quelles lignes de données doivent être retirées de la mémoire cache lorsqu’une nouvelle ligne doit être chargée. Des algorithmes courants incluent le LRU (Least Recently Used, le moins récemment utilisé), FIFO (First In, First Out, premier entré, premier sorti) et LFU (Least Frequently Used, le moins fréquemment utilisé). Chaque politique a ses propres avantages et inconvénients en fonction des types de charges de travail.

-

Écriture dans la mémoire cache : Les opérations d’écriture dans la mémoire cache peuvent être gérées de différentes manières, notamment à travers les politiques d’écriture directe, d’écriture-à-travers et d’écriture de retour. Ces politiques déterminent si les écritures sont effectuées uniquement dans la mémoire cache, dans la mémoire principale en même temps que la mise à jour de la mémoire cache, ou si elles sont d’abord effectuées dans la mémoire cache puis transférées à la mémoire principale ultérieurement.

-

Coût de la cohérence de la mémoire cache : Dans les systèmes multiprocesseurs, assurer la cohérence des données entre les différentes mémoires caches des différents cœurs de processeur peut être un défi majeur. Des protocoles tels que le protocole MESI (Modified, Exclusive, Shared, Invalid, modifié, exclusif, partagé, invalide) sont utilisés pour maintenir la cohérence des caches et garantir que tous les cœurs voient les données mises à jour de manière cohérente.

-

Hiérarchie de mémoire non uniforme (NUMA) : Dans les architectures NUMA, les processeurs sont connectés à différents sous-systèmes de mémoire avec des temps d’accès variables. Cela introduit des défis supplémentaires en matière de gestion de la mémoire et de garantie des performances optimales, car les données doivent être placées de manière stratégique pour minimiser les temps d’accès.

-

Préchargement de la mémoire cache : Certaines architectures de processeurs utilisent des stratégies de préchargement pour anticiper les accès futurs à la mémoire et charger préventivement les données dans la mémoire cache. Cela peut être basé sur des modèles de prédiction d’accès ou des schémas d’accès observés précédemment.

-

Évolution des architectures de mémoire cache : Avec l’augmentation de la complexité des charges de travail et des applications, les concepteurs d’architectures informatiques explorent de nouvelles approches pour améliorer l’efficacité de la mémoire cache. Cela inclut l’utilisation de caches à cohérence de données transactionnelles, de mémoires cache partagées sur des accélérateurs comme les GPU, et même l’exploration de techniques de stockage non volatil dans la hiérarchie de mémoire.

En examinant ces aspects avancés de la hiérarchie de mémoire et de la mémoire cache, nous pouvons apprécier la complexité et l’importance de ces composants dans la conception et l’optimisation des systèmes informatiques modernes. La recherche continue dans ce domaine vise à relever les défis posés par les nouvelles technologies et les exigences croissantes en matière de performances et d’efficacité énergétique.